FPGA implementation of fog-removal using anisotropic diffusion.

Aug 1, 2018

·

1 min read

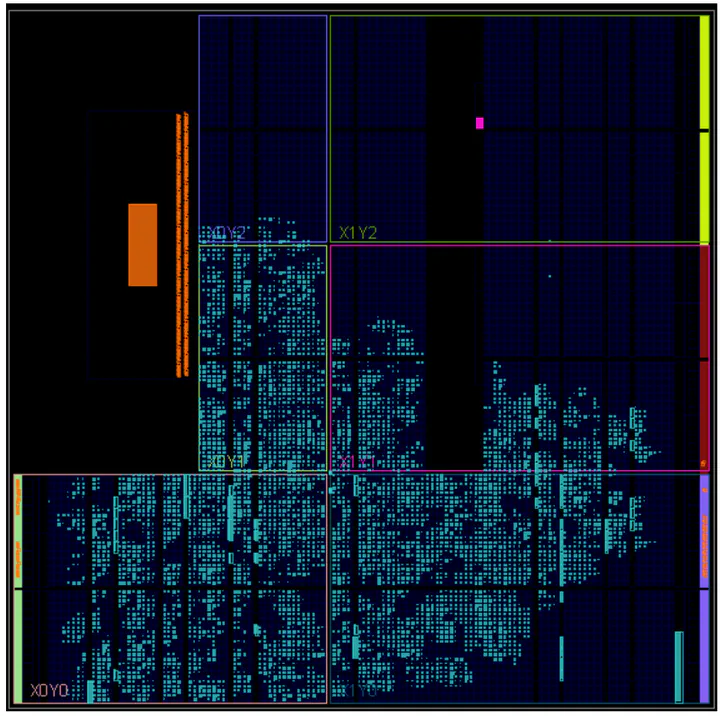

Synthesized hardware

Synthesized hardwareProject Supervisor: Professor Sudipta Mukhopadhyay

Achieved 200 fps processing speed in simulations of synthesizable code for Xilinx Zedboard FPGA for high-speed video processing to remove fog from images using anisotropic diffusion. Simulated and verified implementation from scratch on Vivado HLS, synthesized to RTL, and integrated blocks at the system level using Vivado IP integrator.